QR ကုဒ်

ကြှနျုပျတို့အကွောငျး

ထုတ်ကုန်များ

ကြှနျုပျတို့ကိုဆကျသှယျရနျ

ဖက်စ်

+86-579-87223657

အီးမေး

လိပ်စာ

Wangda လမ်း၊ Ziyang လမ်း၊ Wuyi ကောင်တီ၊ Jinhua မြို့၊ Zhejiang ပြည်နယ်၊ တရုတ်နိုင်ငံ

Semiconductor ထုတ်ကုန်တစ်ခုစီ၏ထုတ်လုပ်ခြင်းသည်ရာနှင့်ချီသောလုပ်ငန်းစဉ်များလိုအပ်သည်။ ထုတ်လုပ်မှုလုပ်ငန်းစဉ်တစ်ခုလုံးကိုအဆင့်ရှစ်ဆင့်ခွဲထားသည်။wafer အပြောင်းအလဲနဲ့ - ကပ်စေခြင်း - photolithography - ကပ်ခြင်း - ပါးလွှာသောရုပ်ရှင်အစစ်ခံ - ကြားဝင် - စမ်းသပ်ခြင်း - ထုပ်ပိုးခြင်း.

![]()

အဆင့် 1:wafer အပြောင်းအလဲနဲ့

Semiconductor ဖြစ်စဉ်များအားလုံးသည်သဲများနှင့်စတင်သည်။ ဘာဖြစ်လို့လဲဆိုတော့သဲထဲမှာရှိတဲ့ဆီလီကွန်မှာရှိတဲ့ဆီလီကွန်ကတော့ wafers ထုတ်လုပ်ဖို့လိုအပ်တဲ့ကုန်ကြမ်းတွေပါ။ Silicon (Si) သို့မဟုတ်ဂယ်လီယမ် (Gallium Arsenide) ဖြင့်ပြုလုပ်ထားသောတစ်ခုတည်းသောကြည်လင်ဆလင်ဒါများကနေလှည့်လည်ကြည့်ရှုသည်။ Purity Silicon ပစ္စည်းများထုတ်ယူရန်အတွက် Silica သဲ, ဆီလီကွန်ဒိုင်အောက်ဆိုဒ်ပါသည့်အထူးပစ္စည်းသည်ဆေးလီယုန်ဒိုင်အောက်ဆိုဒ်နှင့်အတူအထူးပစ္စည်းများလိုအပ်သည့်အထူးပစ္စည်းများလိုအပ်သည်။ Wafer processing သည်အထက်ပါယောင်များကိုလုပ်ခြင်းလုပ်ငန်းစဉ်ဖြစ်သည်။

ingot casting

ပထမ ဦး စွာသဲသည်ကာဗွန်မိုနောက်ဆိုဒ်နှင့်ဆီလီကွန်ကိုခွဲခြားရန်အပူပေးရန်လိုအပ်သည်။ Ultra-hurity electronic grade silicon (ဥပမာ - Si) ရရှိသောအထိလုပ်ငန်းစဉ်ကိုထပ်ခါတလဲလဲပြုလုပ်သည်။ သန့်ရှင်းစင်ကြယ်သောဆီလီကွန်သည်အရည်ထဲသို့အရည်ပျော်သွားပြီး Semiconductor ကုန်ထုတ်လုပ်မှုတွင်ပထမဆုံးခြေလှမ်းဖြစ်သော "INGOT" ဟုခေါ်သော "ingot" ဟုခေါ်သော Crystal Solid Form တစ်ခုတည်းသို့ systifies ။

ဆီလီကွန် Ingots (ဆီလီကွန်တိုင်) ၏ကုန်ထုတ်လုပ်မှုတိကျစွာ (ဆီလီကွန်တိုင်) သည်အလွန်မြင့်မားပြီး nanometer အဆင့်သို့ရောက်ရှိပြီးကျယ်ပြန့်စွာအသုံးပြုသောကုန်ထုတ်လုပ်မှုနည်းလမ်းမှာ CZOCHASKI နည်းလမ်းဖြစ်သည်။

ingot ဖြတ်တောက်ခြင်း

ယခင်အဆင့်ပြီးဆုံးသွားသောအခါ, INGOT ၏စွန်းတိုင်အောင်စိန်နှင့်အတူစိန်နှင့်အတူနှစ်ခုဖြတ်တောက်ရန်လိုအပ်ပါသည်။ INGOT အချပ်သည်အချပ်သည် wafer ၏အရွယ်အစားကိုဆုံးဖြတ်သည်။ ပိုကြီးပြီးပါးလွှာသောအသံများက ပိုမို. အသုံးဝင်သောယူနစ်များအဖြစ်ခွဲခြားနိုင်သည်။ ၎င်းသည်ထုတ်လုပ်မှုကုန်ကျစရိတ်ကိုလျှော့ချရန်ကူညီသည်။ ဆီလီကွန်အင်ဂျင်နီယာကိုဖြတ်တောက်ပြီးနောက် "flat ရိယာ" သို့မဟုတ် "အံသွား" ကိုထပ်ဆင့်လုပ်ဆောင်ရန်လမ်းကြောင်းအဖြစ်သတ်မှတ်ခြင်းကိုလွယ်ကူချောမွေ့စေရန်အချပ်များပေါ်တွင် "area ရိယာ" သို့မဟုတ် "သွား" အမှတ်အသားများကိုထည့်သွင်းရန်လိုအပ်သည်။

wafer မျက်နှာပြင် polishing

အထက်ပါဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်မှရရှိသောအချပ်များကို "Wafers" ဟုခေါ်ဆိုမှုမရှိသော "Burofers" ဟုခေါ်သည်။ ရှင်းလင်းသောကြိုး၏မျက်နှာပြင်သည်မညီမညာဖြစ်နေသောအသံကိုမညီမညာဖြစ်နေသည်။ ထို့ကြောင့်ကြိတ်ခွဲခြင်းနှင့်ဓာတုကိုင်ဆောင်ခြင်းလုပ်ငန်းစဉ်များအားပထမဆုံးအကြိမ်ဖယ်ရှားခြင်းများကို ဦး စွာဖယ်ရှားရန်လိုအပ်ပါသည်။

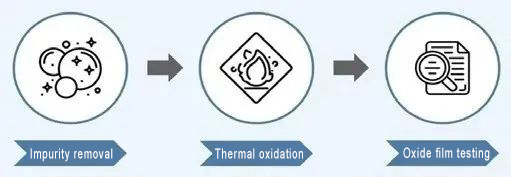

အဆင့် 2: အောက်စီဂျင်

ဓာတ်တိုးခြင်းလုပ်ငန်းစဉ်၏အခန်းကဏ် is သည် wafer ၏မျက်နှာပြင်ပေါ်တွင်အကာအကွယ်ရုပ်ရှင်ကိုဖွဲ့စည်းရန်ဖြစ်သည်။ ၎င်းသည်ဓာတ်အားပေးသူအားဓာတုဗေဒအညစ်အကြေးများမှကာကွယ်ပေးသည်။

ကပ်စေခြင်း လုပ်ငန်းစဉ်၏ပထမအဆင့်မှာအညစ်အကြေးနှင့်ညစ်ညမ်းမှုများကိုဖယ်ရှားရန်ဖြစ်သည်။ အော်ဂဲနစ်ပစ္စည်းအညစ်အကြေးများနှင့်ကျန်နေတဲ့ရေကိုဖယ်ရှားရန်အဆင့်လေးဆင့်လိုအပ်သည်။ သန့်ရှင်းရေးလုပ်ပြီးနောက်ဒီဂရီ 800 မှ 1200 ဒီဂရီစင်တီဂရိတ်စင်တီဂရိတ် (i.e. "silicon dioxide (i.e. " အောက်ဆိုဒ်) တွင် silicon dioxide (i.e. "အောက်ဆိုဒ်) တွင်ထည့်သွင်းနိုင်သည်။ အောက်စီဂျင်သည်အောက်ဆိုဒ်များကို ဖြတ်. ပျံ့နှံ့သွားပြီးဆီလီကွန်နှင့်ကွဲပြားခြားနားသောအထူအမျိုးမျိုးရှိသောအောက်ဆိုဒ်အလွှာတစ်ခုဖြစ်ပေါ်စေရန်၎င်းအထူကိုတိုင်းနိုင်သည်။

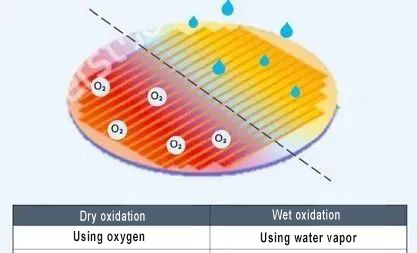

ခြောက်သွေ့သောဓာတ်တိုးခြင်းနှင့်စိုစွတ်ခြင်းနှင့်စိုစွတ်သော oxidiation ဓာတ်တိုးများပေါ်ရှိကွဲပြားခြားနားသော oxidants ပေါ် မူတည်. ဓာတ်တိုးခြင်းဆိုင်ရာဓာတ်တိုးများပေါ် မူတည်. ဓာတ်တိုးခြင်းလုပ်ငန်းစဉ်ကိုခြောက်သွေ့သောဓာတ်တိုးခြင်းနှင့်စိုစွတ်သောဓာတ်တိုးခြင်းသို့ခွဲခြားနိုင်သည်။ ယခင်က Silicon Dioxide layer ကိုထုတ်လုပ်ရန်အောက်စီဂျင်ကို အသုံးပြု. နှေးကွေးသော်လည်းအောက်ဆိုဒ်သည်ပါးလွှာပြီးသိပ်သည်းသည်။ အဆုံးစွန်သောအောက်ဆီဂျင်နှင့်အလွန်ပျော်ဝင်နိုင်သောရေငွေ့များကိုပိုမိုကောင်းမွန်စွာကြီးထွားမှုနှုန်းဖြင့်သွင်ပြင်လက်ခဏာရှိသော်လည်းသိပ်သည်းမှုနည်းပါးသောအတော်လေးအထူအကာအကွယ်အလွှာသည်အတော်လေးထူထပ်သောအကာအကွယ်အလွှာဖြစ်သည်။

oxidant အပြင် silicon dioxide layer ၏အထူကိုအကျိုးသက်ရောက်စေသောအခြား variable များလည်းရှိသည်။ ပထမ ဦး စွာ Wafer ဖွဲ့စည်းပုံ, ၎င်း၏မျက်နှာပြင်ချို့ယွင်းချက်များနှင့်ပြည်တွင်းချို့ယွင်းချက်များနှင့်ပြည်တွင်းရေး doping အာရုံစူးစိုက်မှုသည်အောက်ဆိုဒ်အလွှာမျိုးဆက်သစ်နှုန်းကိုအကျိုးသက်ရောက်လိမ့်မည်။ ထို့အပြင်ဓာတ်တိုးခြင်းပစ္စည်းကိရိယာများမှထုတ်လုပ်သောဖိအားနှင့်အပူချိန်ပိုမိုမြင့်မားလေ, အောက်ဆိုဒ်အလွှာပိုမိုမြန်ဆန်လေလေဖြစ်သည်။ ဓာတ်တိုးမှုဖြစ်စဉ်တွင် wafer ကိုကာကွယ်ရန်နှင့်ဓါတ်တိုးခြင်းဒီဂရီခြားနားချက်ကိုလျှော့ချရန်ယူနစ်ရှိ wafer ၏အနေအထားအရ Dummy Sheet ကိုသုံးရန်လိုအပ်သည်။

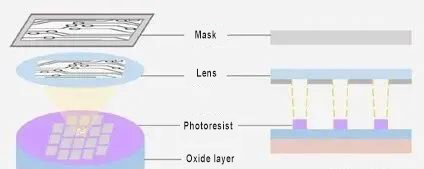

အဆင့် 3: photolithography

photolithography သည် circuit ပုံစံကို "print" ကို "print" ကိုအလင်းမှတဆင့်အလင်းပေါ်သို့ "ပုံနှိပ်" ရန်ဖြစ်သည်။ Semiconductor ထုတ်လုပ်မှုအတွက်လိုအပ်သည့်လေယာဉ်မြေပုံကိုအသုံးပြုရန်လိုအပ်သလိုနားလည်နိုင်သည်။ circuit ပုံစံကိုပိုမိုမြင့်မားလေလေ, အဆင့်မြင့် photolithography နည်းပညာမှတစ်ဆင့်အောင်မြင်ရမည့်ချောပ်ချက်ကိုပေါင်းစည်းလေလေဖြစ်သည်။ အထူးသဖြင့် Potolithography ကိုအဆင့်သုံးဆင့်ခွဲထားနိုင်သည်။

အထပ်

wafer ပေါ်တွင် circuit တစ်ခုကိုဆွဲခြင်း၏ပထမခြေလှမ်းမှာ Photoresist ကိုအောက်ဆိုဒ်အောက်ဆိုဒ်တွင်ပါ 0 င်ရန်ဖြစ်သည်။ Photoresist သည် Wafer ကို၎င်း၏ဓာတုဗေဒဆိုင်ရာဂုဏ်သတ္တိများပြောင်းလဲခြင်းဖြင့် "ဓာတ်ပုံစက္ကူ" ကိုပြုလုပ်သည်။ Photoresist အလွှာကို wafer ၏မျက်နှာပြင်ပေါ်ရှိ Photoresist Layer နှင့် Peter ကိုပိုမိုပါးလွှာ။ ပုံနှိပ်နိုင်သည့်ပုံစံများကိုပိုမိုကောင်းမွန်သောပုံစံဖြင့်ပြုလုပ်နိုင်သည်။ ဤအဆင့်ကို "spin coating" နည်းလမ်းဖြင့်ပြုလုပ်နိုင်သည်။ Light (Ultraviolet) ဓာတ်ပြုမှုကွဲပြားမှုအရ Photoresists ကိုအမျိုးအစားနှစ်မျိုးခွဲခြားနိုင်သည်။ ယခင်ကယခင်ကထိတွေ့ခြင်းနှင့်ထိတွေ့ပြီးနောက်ပြိုကွဲသွားပြီးပျောက်ကွယ်သွားလိမ့်မည်။

ထိတွေ့ခြင်း

Photoresist ရုပ်ရှင်ကို Wafer ပေါ်တွင်ဖုံးအုပ်ပြီးနောက်အလင်းထိတွေ့မှုကိုထိန်းချုပ်ခြင်းဖြင့်တိုက်နယ်ပုံနှိပ်ခြင်းဖြင့်တိုက်နယ်ပုံနှိပ်ခြင်းဖြင့်ပြီးစီးနိုင်သည်။ ဤလုပ်ငန်းစဉ်ကို "ထိတွေ့မှု" ဟုခေါ်သည်။ ကျနော်တို့ထိတွေ့ပစ္စည်းကိရိယာများမှတဆင့်အလင်းဖြတ်ကူးနိုင်ပါတယ်။ အလင်းသည် circuit ပုံစံပါ 0 င်သောမျက်နှာဖုံးကိုဖြတ်သန်းသွားသောအခါ circuit ကို photoresist ရုပ်ရှင်ဖြင့်ဖုံးအုပ်ထားသော wafer ပေါ်တွင်ပုံနှိပ်နိုင်သည်။

ထိတွေ့မှုလုပ်ငန်းစဉ်အတွင်းပုံနှိပ်ထုတ်ဝေသည့်ပုံစံတွင်ပိုမိုကောင်းမွန်သောအစိတ်အပိုင်းများပိုမိုများပြားလာလေ, ဤနယ်ပယ်တွင်လက်ရှိအာရုံစူးစိုက်မှုကိုဆွဲဆောင်နိုင်သည့်နည်းပညာအသစ်သည် Euv lithography ဖြစ်သည်။ Lam Research Group သည် Strategic Partysist Technology နှင့် Asml နှင့် IMEC တို့တွင်ခြောက်သွေ့သောရုပ်ရှင်တွန်းချက်အသစ်ကိုပူးတွဲတီထွင်ခဲ့သည်။ ဤနည်းပညာသည် Euv lithography ထိတွေ့မှုဖြစ်စဉ်ကိုအရှိန်မြှင့်ခြင်းအားဖြင့် EUV lithography ထိတွေ့မှုလုပ်ငန်းစဉ်ကိုတိုးတက်အောင်လုပ်ခြင်းကိုပိုမိုကောင်းမွန်စေနိုင်သည်။

တိုးတက်ရေး

ထိတွေ့မှုအပြီးခြေလှမ်းသည် developer ကို wafer ပေါ်ရှိဖြန်းရန်ဖြစ်သည်, ရည်ရွယ်ချက်မှာ plated circuit ပုံစံကိုဖော်ထုတ်နိုင်ရန်ရည်ရွယ်ချက်မှာ Photoresist ကိုဖယ်ရှားရန်ဖြစ်သည်။ ဖွံ့ဖြိုးတိုးတက်မှုပြီးဆုံးသွားသောအခါ၎င်းသည် circuit diagram ၏အရည်အသွေးကိုသေချာစေရန်တိုင်းတာခြင်းဆိုင်ရာပစ္စည်းကိရိယာများနှင့် optical microscopes များကစစ်ဆေးရန်လိုအပ်သည်။

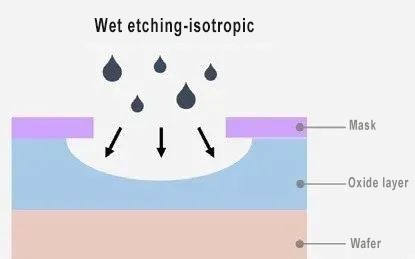

အဆင့် 4: actching

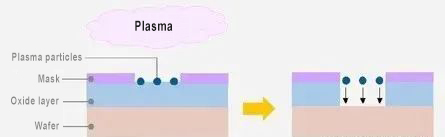

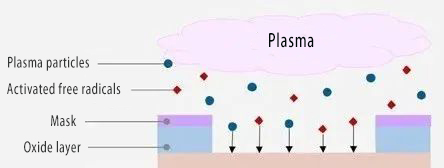

circuit dorgram ကို photolithography ကိုပြီးစီးပြီးနောက် Semiconductor Circuit film ကိုသာဖယ်ရှားပစ်ရန် actching process ကို အသုံးပြု. Semiconductor circuit onram ကိုသာထားခဲ့ပါ။ ဤသို့ပြုလုပ်ရန်, အရည်, ဓာတ်ငွေ့သို့မဟုတ်ပလာစမာကိုရွေးချယ်ထားသောပိုလျှံအစိတ်အပိုင်းများကိုဖယ်ရှားရန်အသုံးပြုသည်။ အသုံးပြုသောပစ္စည်းများပေါ် မူတည်. အဓိကကျသောနည်းလမ်းနှစ်ခုရှိသည်။

စိုစွတ်သော etting

အောက်ဆိုဒ်များကိုဖယ်ရှားရန်ဓာတုဗေဒဆိုင်ရာဖြေရှင်းနည်းများကို အသုံးပြု. စိုစွတ်သော etching သည်ကုန်ကျစရိတ်သက်သာသည့်, သို့သော်စိုစွတ်သောစွဲကပ်မှုသည် ITOPOPIC ဖြစ်သည်။ ၎င်းသည်မျက်နှာဖုံး (သို့မဟုတ်အထိခိုက်မခံသောရုပ်ရှင်) ကိုစွဲစေသည့်အောက်ဆိုဒ်ရိုက်ကူးမှုနှင့်လုံးဝမပေါင်းသင်းရန်ဖြစ်ပေါ်စေသည်။

ခြောက်သွေ့သော ကပ်ခြင်း

ခြောက်သွေ့သောစွဲမှုကိုမတူညီသောအမျိုးအစားသုံးမျိုးခွဲခြားနိုင်သည်။ ပထမ ဦး ဆုံးအနေဖြင့်ဓာတ်ငွေ့များ (အဓိကအားဖြင့်ဟိုက်ဒရိုဂျင်ဖလိုရိုက်) ကိုအသုံးပြုသောဓာတုကိုင်ကြိုးဖြစ်သည်။ စိုစွတ်သော etching ကဲ့သို့ပင်ဤနည်းလမ်းသည် isotropic ဖြစ်သည်။ ဆိုလိုသည်မှာကောင်းမွန်သောစွဲလမ်းမှုအတွက်မသင့်တော်ပါ။

ဒုတိယနည်းလမ်းမှာ Plasma ရှိအိုင်းယွန်းများကို plasma ရှိအိုင်းယွန်းများကိုသက်ရောက်စေပြီးဖယ်ထုတ်ရန်နှင့်ဖယ်ရှားရန်အသုံးပြုသည်။ anisotropic atching method method တစ်ခုအနေဖြင့် sputtering actuttering သည်အလျားလိုက်နှင့်ဒေါင်လိုက်လမ်းညွှန်များတွင်ကွဲပြားခြားနားသောစွဲမှုနှုန်းများရှိသည်။ သို့သော်ဤနည်းလမ်း၏အားနည်းချက်မှာ `` အမြန်နှုန်းနှေးခြင်းသည်နှေးကွေးနေခြင်းကြောင့်အိုင်းတိုက်မှုကြောင့်ဖြစ်ပေါ်လာသောရုပ်ပိုင်းဆိုင်ရာတုံ့ပြန်မှုများအပေါ်လုံးဝမှီခိုနေသောကြောင့်ဖြစ်သည်။

ပြီးခဲ့သည့်တတိယနည်းလမ်းသည်အိုင်းရစ်မှု ion ion ion (Rie) ဖြစ်သည်။ Rie သည် ionization ရုပ်ပိုင်းဆိုင်ရာစွဲလမ်းမှုအတွက်ပလာစမာကိုအသုံးပြုနေစဉ် Plasma ကိုအသုံးပြုနေစဉ် Plasma activation ပြီးနောက်အခမဲ့အစွန်းရောက်များကိုထုတ်ပေးသည်။ ပထမနည်းစနစ်နှစ်ခုထက်ကျော်လွန်သောအလွဲသုံးစားမှုများအပြင် Rie သည်တိကျသောပုံစံကိုရယူရန် ionotropic ဝိသေသလက္ခဏာများကိုအသုံးပြုနိုင်သည်။

ယနေ့တွင်ခြောက်သွေ့သောစွဲကပ်မှုသည်ကောင်းမွန်သော semiconductor circuits ၏အထွက်နှုန်းကိုတိုးတက်စေရန်ကျယ်ကျယ်ပြန့်ပြန့်အသုံးပြုခဲ့သည်။ အပြည့်အဝ - wafer atching atching နှင့် speeting တိုးပွားလာခြင်းနှင့်အတူတိုးပွားလာခြင်းနှင့်အလွဲသုံးစားမှုအလွဲသုံးစားမှုတိုးပွားလာခြင်းနှင့်ယနေ့အဆင့်မြင့်ခြောက်သွေ့သောစွဲချက်ပစ္စည်းကိရိယာများသည်စွမ်းဆောင်ရည်မြင့်မားသောအဆင့်မြင့်ယုတ္တိဗေဒနှင့်မှတ်ဉာဏ်ချစ်ပ်များထုတ်လုပ်ခြင်းကိုထောက်ခံသည်။

Vetek Semiconductor သည်တရုတ်ထုတ်လုပ်သူဖြစ်သည်Tantalum carbide အပေါ်ယံ, Silicon carbide အပေါ်ယံပိုင်း, အထူးဂိဒ်, ဆီလီကွန်ကာဘက်ကာဗွန်ကြွေထည်နှင့်အခြား semiconductor ceramics။ Vetek Semiconductor သည် SicMonductor Industry အတွက်အမျိုးမျိုးသော Sic Wafer ထုတ်ကုန်များအတွက်အဆင့်မြင့်ဖြေရှင်းချက်များပေးရန်ကတိကဝတ်ပြုထားသည်။

အထက်ပါထုတ်ကုန်များကိုသင်စိတ်ဝင်စားပါကကျွန်ုပ်တို့အားတိုက်ရိုက်ဆက်သွယ်ပါ။

MOB: + 86-180 6922 0752

WhatsApp: +86 180 6922 0752

အီးမေးလ် - Anny@veteksemi.com

+86-579-87223657

Wangda လမ်း၊ Ziyang လမ်း၊ Wuyi ကောင်တီ၊ Jinhua မြို့၊ Zhejiang ပြည်နယ်၊ တရုတ်နိုင်ငံ

မူပိုင်ခွင့် © 2024 WuYi TianYao Advanced Material Tech.Co.,Ltd. မူပိုင်ခွင့်ကိုလက်ဝယ်ထားသည်။

Links | Sitemap | RSS | XML | ကိုယ်ရေးအချက်အလက်မူဝါဒ |